依據歐盟施行的個人資料保護法,我們致力於保護您的個人資料並提供您對個人資料的掌握。 我們已更新並將定期更新我們的隱私權政策,以遵循該個人資料保護法。請您參照我們最新版的 隱私權聲明。

本網站使用cookies以提供更好的瀏覽體驗。如需了解更多關於本網站如何使用cookies 請按 這裏。

21Jun.2023

膜厚儀

半導體製程順序大公開!專家用11步驟告訴你,專業技術大解密!

| 目錄 1.半導體製程是什麼? 2.半導體製程中使用到的主材料有哪些? 3.半導體製程順序大公開! 4.粒徑分析及膜厚量測在半導體製程中,扮演的角色為何? |

許多人對於半導體產業不熟悉,尤其是對半導體製程的概念更是一知半解?!其實,主要是用來製作晶片的半導體製程,是需要透過一系列的專業步驟與搭配粒徑以及饃厚量測後,才能被完整的運用在各個產業之中。若你對於半導體製程還是有許多疑問的話,不妨就一起透過本篇專家的講解來了解吧!

半導體製程是什麼?

所謂的「半導體」,其實就是指一種材料。且其具有介於導體(如:銅和鋁)和絕緣體(如:塑料和橡膠)之間的導電特性。而「半導體」的導電性能,可通過施加外部電場或調整其內部電荷態進行控制。當「半導體」受到外部激勵(如:電場、熱能或光照)時,價帶中的電子可以被激發到傳導帶,就會形成自由移動的電子和正空穴(缺少電子的位置)。

這些自由移動的電子和空穴,完整貢獻了半導體的導電性。通過控制半導體材料中的電子和空穴的數量和移動性,可實現對電流和電壓的精確控制,這是半導體器件(如:二極體、晶體管和集成電路)的基礎。而「半導體」的特性,使其在現代電子技術中扮演了重要的角色。半導體器件的不同組合和配置可以實現各種功能,從電腦和手機到家用電器和自動車等各種應用。

半導體製程中使用到的主材料有哪些?

「半導體」材料中,最常見的例子:是矽(silicon),而「矽」也是製造集成電路的主要材料。除此之外,還有其他半導體材料,如:砷化鎵(gallium arsenide)、砷化銦(indium arsenide)和碲化鎵(gallium telluride)等材料。

「半導體」的導電性質,與其晶體結構、電子能帶結構有關。在純淨的「半導體」中,其電子能帶結構可以劃分為價帶(valence band)和傳導帶(conduction band);價帶中的電子填滿了,而傳導帶中則有較少的電子。兩者之間的能隙(band gap)決定了材料的導電特性。

半導體製程順序大公開!

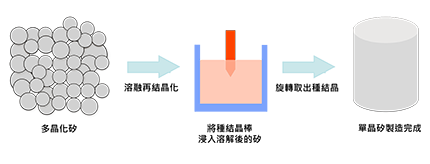

➡️ STEP1. 單晶矽製造

首先是「單晶矽製造」,製造晶錠作為製造晶圓的基板。多晶矽與硼酸(B)和磷(P)一起放入石英坩堝中,在高溫下熔化。將種晶棒浸入熔融矽液面,邊旋轉邊緩慢拉起,即可完成與種晶具有相同原子排列的單晶錠。

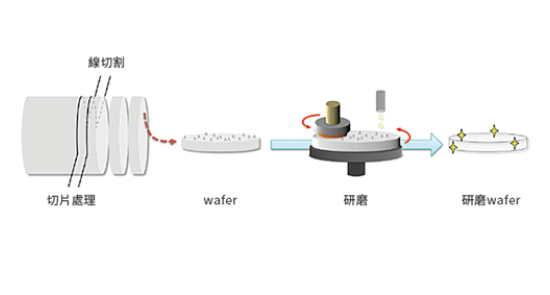

➡️ STEP2. 晶圓 wafer 製作

接下來,是通過減薄鑄錠來製造晶圓的過程。使用稱為線鋸將剛製成的鋼錠切成薄片,稱為晶圓。由於切割後的晶圓表面存在凹凸不平,故通過稱為研磨(粗拋光)、蝕刻(化學拋光)和拋光(鏡面拋光)的拋光工藝去除不平坦。並讓拋光後的晶圓厚度符合SEMI標準等標準,例如:12英寸的晶圓指定厚度為775μm±20μm。

| 📖 量測製程範例 | 對應機種 |

|---|---|

| in-situ膜厚量測->> | 分光干涉式wafer晶圓測厚儀SF-3 |

| 研磨後貼合wafer厚度量測->> | |

| 研磨液粒徑、界達電位->> | 界達電位粒徑分析儀ELSZ |

| wafer表面電位->> |

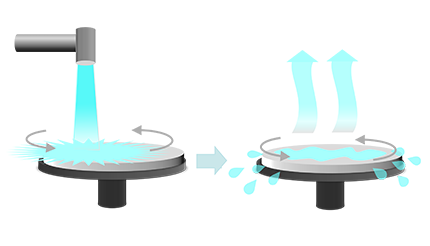

➡️ STEP3. 晶圓 wafer 洗淨

清潔晶片,主要是以去除沾附在表面上的異物。 晶圓上的異物,會導致後續的晶體生長和光刻工藝出現缺陷。 清洗時,用雙氧水、鹽酸、氫氟酸等清洗液去除晶圓上的顆粒、金屬和有機物。之後再使用非常乾淨的超純水,清洗化學溶液後旋轉乾燥。但是如果它仍然是濕的,它會吸收空氣中的顆粒,即使洗過也會使它再次變髒。

| 📖 量測製程範例 | 對應機種 |

|---|---|

| wafer表面電位->> | 界達電位粒徑分析儀ELSZ |

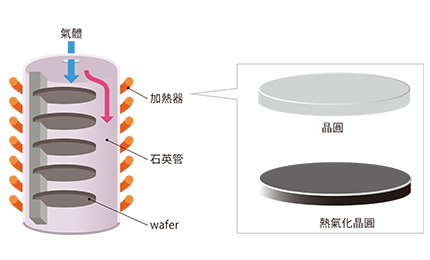

➡️ STEP4. 晶圓 wafer 表面氧化

在晶圓表面氧化過程中,通過熱處理形成高質量的表面氧化膜。 氧化設備主要有立式爐、臥式爐、RTP設備,在稱為氧化爐的電爐中,升溫(約800℃以上),通入含氧氣體,使氧化膜生長。

| 📖 量測製程範例 | 對應機種 |

|---|---|

| 成膜後wafer面內膜厚分布->> | 晶圓厚度量測&產線上膜厚量測設備TE |

➡️ STEP5. 配線圖案

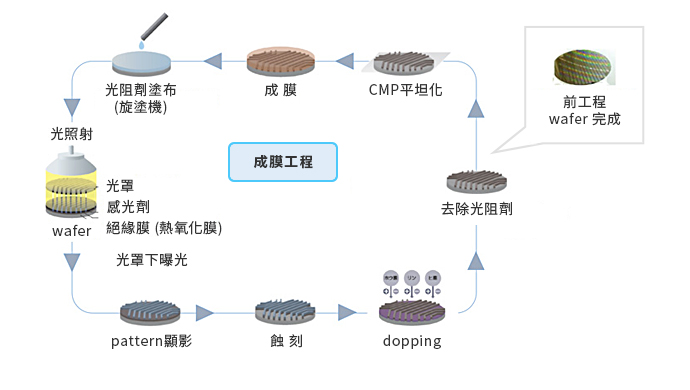

熱氧化後,在晶圓上塗上光刻膠,通過曝光/顯影、刻蝕、清洗、CMP工藝在晶圓上形成圖形。

| 📖 量測製程範例 | 對應機種 |

|---|---|

| in-situ膜厚量測->> | 分光干涉式wafer晶圓測厚儀SF-3 |

| in-situ膜厚量測->> | 晶圓厚度量測&產線上膜厚量測設備TE |

➡️ STEP6. 晶圓 wafer 測試

晶圓探測器,可測試晶圓上形成的所有晶片的電氣特性。這個晶圓測試,將直接分揀出好的晶圓和壞的晶圓。

➡️ STEP7. 晶圓 wafer 貼合

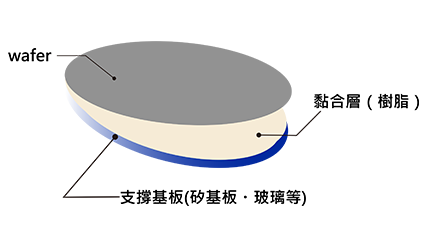

在晶圓減薄工藝中,晶圓附著在矽或玻璃等支撐基板上,以便於運輸過程中的處理。還提出了用夾在它們之間的樹脂(黏合劑層)進行接合的接合方法,與最近將晶片彼此直接接合的接合方法。

| 📖 量測製程範例 | 對應機種 |

|---|---|

| 貼合wafer厚度量測->> | 分光干涉式wafer晶圓測厚儀SF-3 |

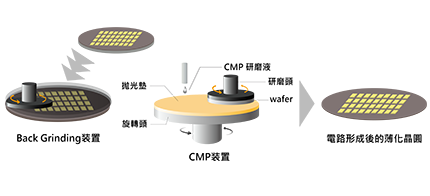

➡️ STEP8. Back grinding

在晶圓表面完成圖形後,對晶圓的整個背面進行研磨以降低厚度。需要降低磨削後整個晶圓的厚度不均,需要將厚度不均控制在很小的範圍內。

| 📖 量測製程範例 | 對應機種 |

|---|---|

| in-situ膜厚量測->> | 分光干涉式wafer晶圓測厚儀SF-3 |

| 研磨後貼合wafer厚度量測->> | |

| CMP研磨液粒徑、界達電位->> | 界達電位粒徑分析儀ELSZ |

| wafer表面電位->> |

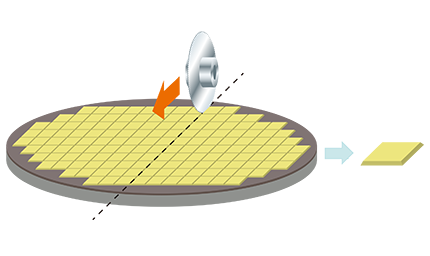

➡️ STEP9. Wafer 切割

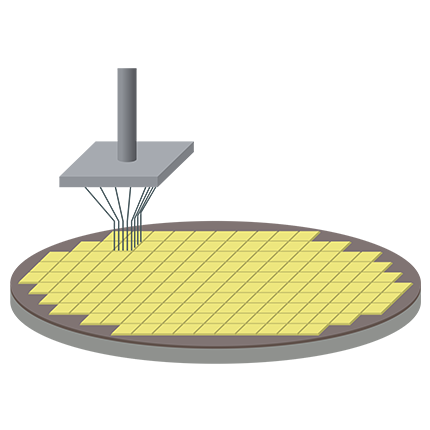

將前工序中生產的晶圓,被分離成單獨的 IC 芯片並密封在封裝中,這種將晶片製成小塊的過程稱為「切割」。

在切割時,主要由金剛石製成的圓形旋轉刀片(劃片鋸)高速旋轉,切割時再用純淨水冷卻並沖走切屑。

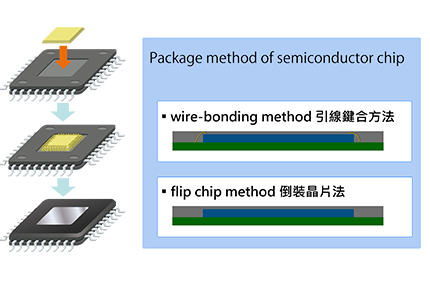

➡️ STEP10. 封裝

完成的晶片,通過引線鍵合和重新分佈層路由到封裝基板、矽支撐基板等。然後再用諸如環氧樹脂封裝晶片。

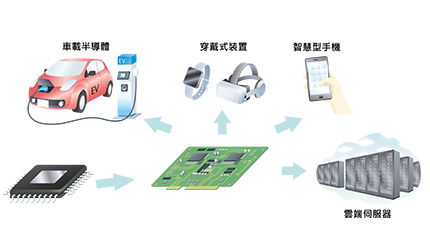

➡️ STEP11. 部件完成

完成的半導體封裝,被整合到各個領域的產品中,例如:汽車、智能手機、IoT 設備、雲數據中心和 AI 相關產品。

粒徑分析及膜厚量測在半導體製程中,扮演的角色為何?

由上述可得知,半導體製程從長晶到完成部件為止,需要經過多道製程。每一道製程的良率,都關乎最後產品的性能。其中,例如:研磨液的界達電位、粒徑影響研磨的過程,研磨製程後及貼合、表面氧化等也都需要監控膜厚。

「半導體」多道製程中,都有減薄、平坦化的過程,此工法又稱為「化學機械研磨,Chemical-Mechanical Polishing」,簡稱為 CMP。想知道更多有關於 CMP 的相關知識,也可以參考《CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!》這篇文章喔!

📖 閱讀更多相關文章📖

📖《CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!》相關產品

其他相關訊息

-

06.Dec.2022

CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!

-

01.Aug.2022

【薄膜厚度量測】『顯微分光法』與『橢圓偏光法』有什麼不同?

-

25.Mar.2025

半導體薄膜製程是什麼?6大技術提升良率,專業應用優勢多!