依據歐盟施行的個人資料保護法,我們致力於保護您的個人資料並提供您對個人資料的掌握。 我們已更新並將定期更新我們的隱私權政策,以遵循該個人資料保護法。請您參照我們最新版的 隱私權聲明。

本網站使用cookies以提供更好的瀏覽體驗。如需了解更多關於本網站如何使用cookies 請按 這裏。

23Jan.2024

膜厚儀

矽穿孔(TSV)孔徑底材膜厚量測介紹:深入了解TSV製程及原理,知道製品優勢在那裡

| 目錄 1.TSV矽通孔技術是什麼?跟膜厚量測有關係嗎? a.TSV 配合 3D IC 製作,形成半導體製程工藝 2.TSV孔徑底材膜厚量測製程差異比較 a.TSV 與 TGV 差異 3.TSV孔徑底材膜厚量測對製程重要嗎? 4.TSV孔徑底材膜厚量推薦 5.TGV開孔量測推薦 |

在現今科技快速發展之下,TSV(Through-Silicon Via)技術已成為三維積體電路(3D IC)中不可或缺的一環。然而,當TSV的尺寸與結構也越來越精細,這對其孔徑底材膜厚的量測也提出了新的挑戰。TSV孔徑底材膜厚量測,對於確保TSV製程的品質與可靠性至關重要。如果你對於TSV孔技術還是一知半解的話,不妨就透過本文來了解其技術創新發展吧!

TSV矽通孔技術是什麼?跟膜厚量測有關係嗎?

所謂的「TSV」,就是「Through Silicon Via」的英文縮寫。就字義上的翻譯來看,為「直通矽晶穿孔」,至於其定義於作用為何,則要從半導體的封裝技術開始說起。就像我們一般在貨物堆積放載的道理一樣,如果是單一物品放置則是一維、 兩個的時候就會朝單一方向成為二維放置,故物品越多後就會成為三維排列的體積來增加空間使用率。

而半導體晶片堆疊,也是相同的概念。

當晶片的功能越來越強大、越來越複雜後,其單一個計算單元已無法滿足的要求,這時候將會增加各種不同的單元以擴張晶片的計算能力。

這時候除了主運算功能的晶片外,還可依據實際需求會有很多周邊功能的晶片,並以二維的方式分散在其周圍。

TSV 配合 3D IC 製作,形成半導體製程工藝

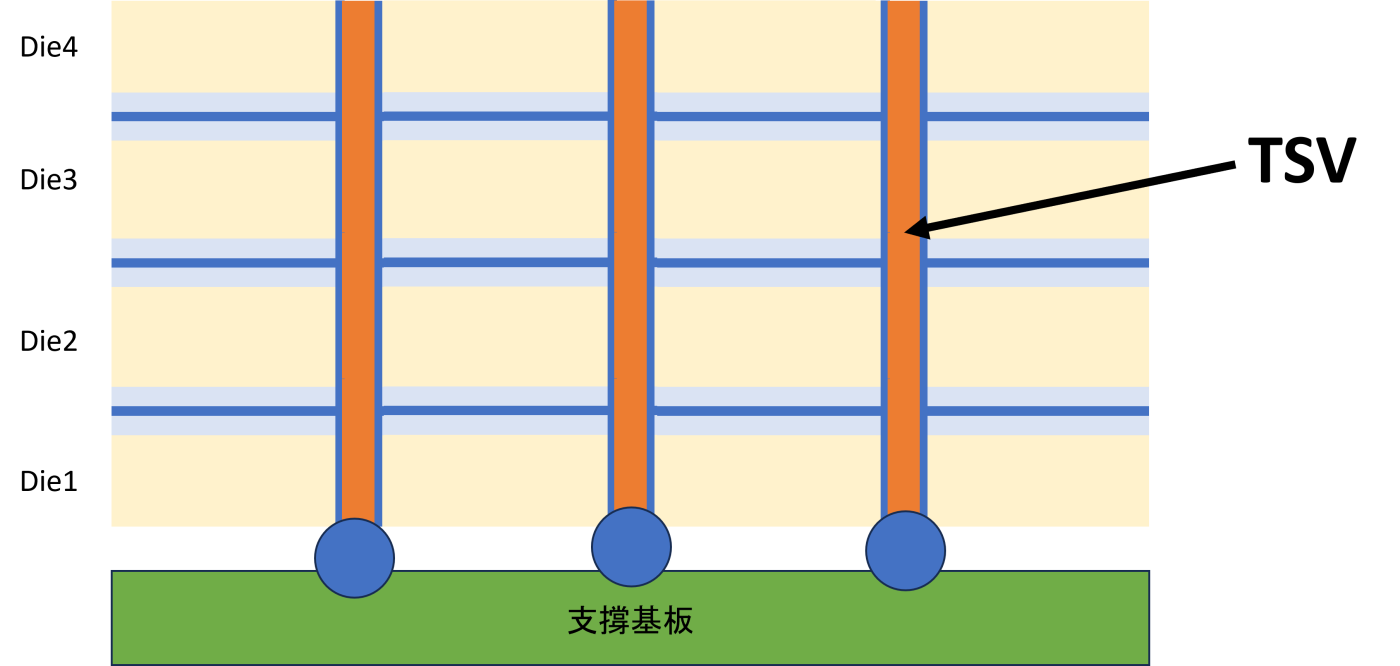

當越多晶片單元需要存在的情況下,則可以考慮最佳效率的前提下,故而產生往三維堆疊所為的「3D IC」一詞;而TSV則是在配合「3D IC」的製作下,所需的一種半導體製程工藝。你可以想像一下,當我們在蓋房子的時候是一層一層往上蓋時,其樓層與樓層之間要如何能夠使人員及物品能夠流通。

這時候會有樓梯或是電梯,來讓人員或是物品能夠上下樓所使用。

就如同蓋房子般,各單元晶片以一層一層堆疊完成後,各晶片在「3D IC」對疊後,如何讓上下兩層的電流訊號可以流動?

TSV就是為此所存在的工藝,並針對以矽為基底的半導體,在上層要往下層、下層往上層流通電流訊號時,我們則在其上層矽基板開孔。而在開孔後,會需要再填入銅等高導電係數的材料後,其上層或下層的電流訊號就可以順利的流通,故TSV就像是半導體晶片中流通的「電梯」。

利用TSV封裝的好處,是可將半導體的面積從二維轉向三維體積,並大大節省半導體的面積。

在節省半導體的面積後,其電流訊號的流動距離,也可以大大的減少訊號的傳輸的速度也會變快,進而提高晶片在運算的效率。

而電流訊號流動的距離減少後,也會因線路的阻抗而減少,其為阻抗所產生的熱損失也跟著減少,故晶片的效率也跟著提高。

TSV孔徑底材膜厚量測製程差異比較

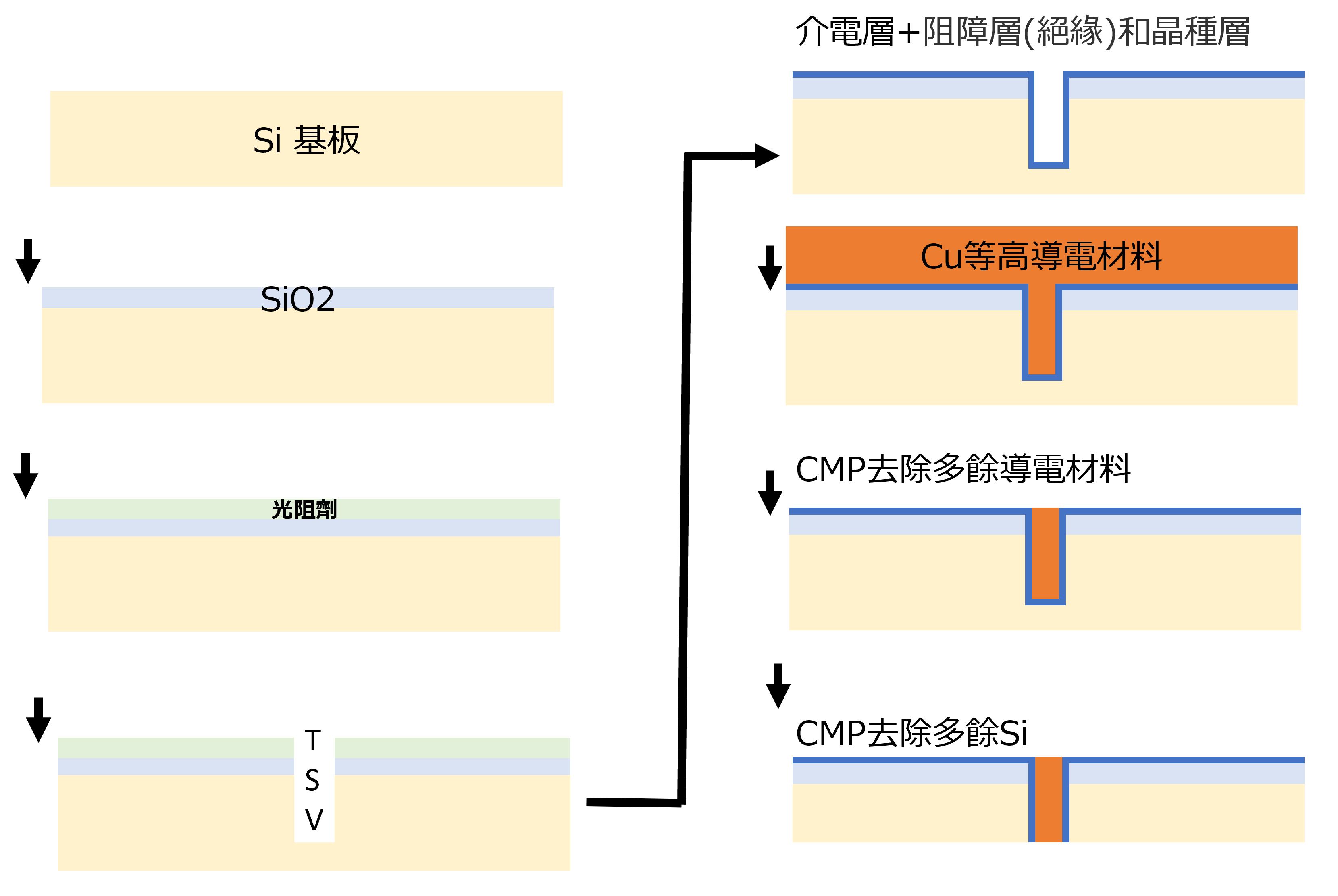

TSV製程,大概會經過下面幾個步驟:STEP1. 在矽晶圓上附上SiO2及光阻劑

STEP2. 蝕刻後開孔,製成想要的形狀、開孔大小等等

STEP3. 以氣相沉積或原子層沉積法,沉積介電層、阻障層、晶種層

STEP4. 填充入Cu等高導電材質後,以CMP去除多餘多餘的金屬層

STEP5. 以CMP去除多餘的Si層形成流通的孔洞

圖.TSV製程示意圖

在做TSV開孔後,會有很多需要注意的,例如:TSV孔位要開多大才夠滿足需求、TSV孔洞的形狀等等也會影響電流的流動。而這是取決於晶片電流大小,當晶片電流相當大的時候,為了使大電流流過TSV的開孔,則開孔會越大。當開孔越大,就必須考慮矽基板本身的材料強度。相反的如果開孔數量少,又偏向某一位置,則造成的單一位置的熱累積過大損失過多,故在做TSV開孔時工程師需要經過仔細地計算後再來決定開孔的位置分布、數量及大小。

在目前半導體技術的演進下,不會只有針對矽基板來做開孔。而是針對不同使用目的的半導體晶片,也有提出比矽強度更強,能承受更多開孔數量或適用於通訊時,可以承受更高頻的訊號如玻璃來做為封裝材料;一般稱為TGV(Through Glass Via),但不論使用哪種材料其開孔的目的不便,都是為了讓IC能夠計算速度更快更好。

TSV 與 TGV 差異

TSV 和 TGV 皆是在3D封裝領域中,用於實現多晶片堆疊和連接的技術。但兩者的基本材料和製程步驟有所不同,TSV 主要使用在矽晶片上;而 TGV 則使用在玻璃基板上,具有更大的應用靈活性。| TSV製程(Through Silicon Via) | TGV製程(Through Glass Via) | |

|---|---|---|

| TGV製程(Through Glass Via) | TSV 是一種通過矽晶片的垂直通孔,將多個晶片層進行堆疊和連接的技術 | TGV 是一種通過玻璃基板的垂直通孔,用於將多個晶片層堆疊在一起 |

| 製程步驟 | TSV 製程包括在矽晶片上鑽孔、填充導體材料、進行薄膜製程等步驟,以建立三維通孔 | TGV 製程涉及使用雷射等技術在玻璃基板上製造通孔,然後進行導體填充等步驟,最終實現多層連接。目前在TGV方面,也有使用雷射替代蝕刻液作為開孔方式 |

| 應用 | TSV 技術主要應用於3D IC(三維積體電路)和3D封裝,有助於提高晶片性能和節省空間 | TGV 技術,通常會應用於柔性顯示器、穿戴式裝置等需要輕薄、彎曲性能的產品 |

| 優勢 | TGV 的製程相對簡單,且能夠提供更高的製程尺寸和更低的製造成本 |

TSV孔徑底材膜厚量測對製程重要嗎?

一般來說,TSV與TGV的開孔,都是以蝕刻的方式來做進行。是先將上下兩層相互bonding後,再來對上層的矽晶圓針對指定的位置,來做蝕刻TSV開孔(以及TGV開孔)的動作。而在蝕刻後,是否完全將TSV(TGV)的孔位貫通,則是一重要需監控的項目。而貫通後其下層的絕緣氧化層是,否受到TSV(TGV)蝕刻的影響,使得薄度變薄也是需要監控的項目。如果TSV(TGV)的蝕刻製程,沒有做膜厚控制的話,就很容易造成下層絕緣氧化層受到損壞。在厚度損厚的情況下,其絕緣能力下降,輕則造成漏電流增加晶片發熱效率下降,重則有可能使的晶片因斷路而燒毀。故絕緣層膜厚等量測,是相當重要的監控項目之一!

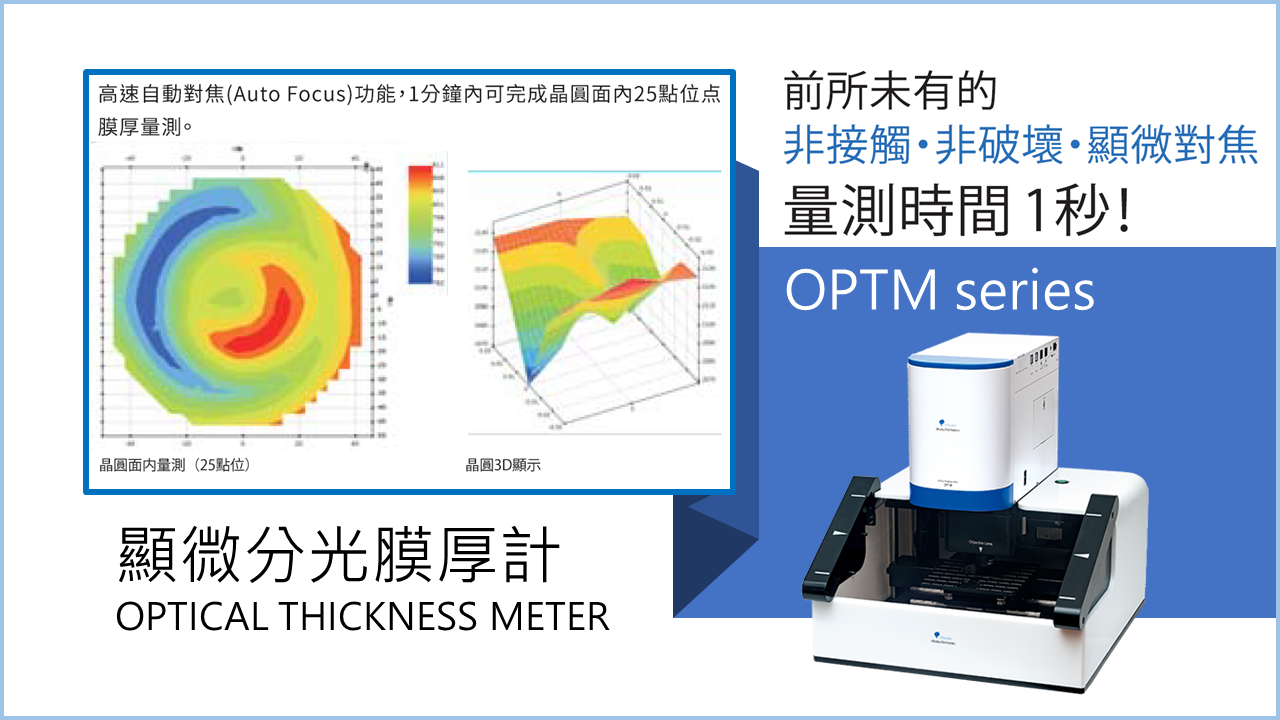

TSV孔徑底材膜厚量推薦

臺灣大塚科技的OPTM系列,在使用40倍的Lens情況下,能將膜厚量測光斑最小微縮到約3um。並可針對TGV幾十um的開孔時,能深入到TGV開孔的底層去量測底層膜厚的厚度。還可依據不同條件下,最大可能對應到TGV孔位及深度最大深寬比6下做非接觸、非破壞且快速的膜厚量測,提供製程工程師相當有助益的膜厚量測結果。👉商品推薦:顯微分光膜厚量測儀OPTM series

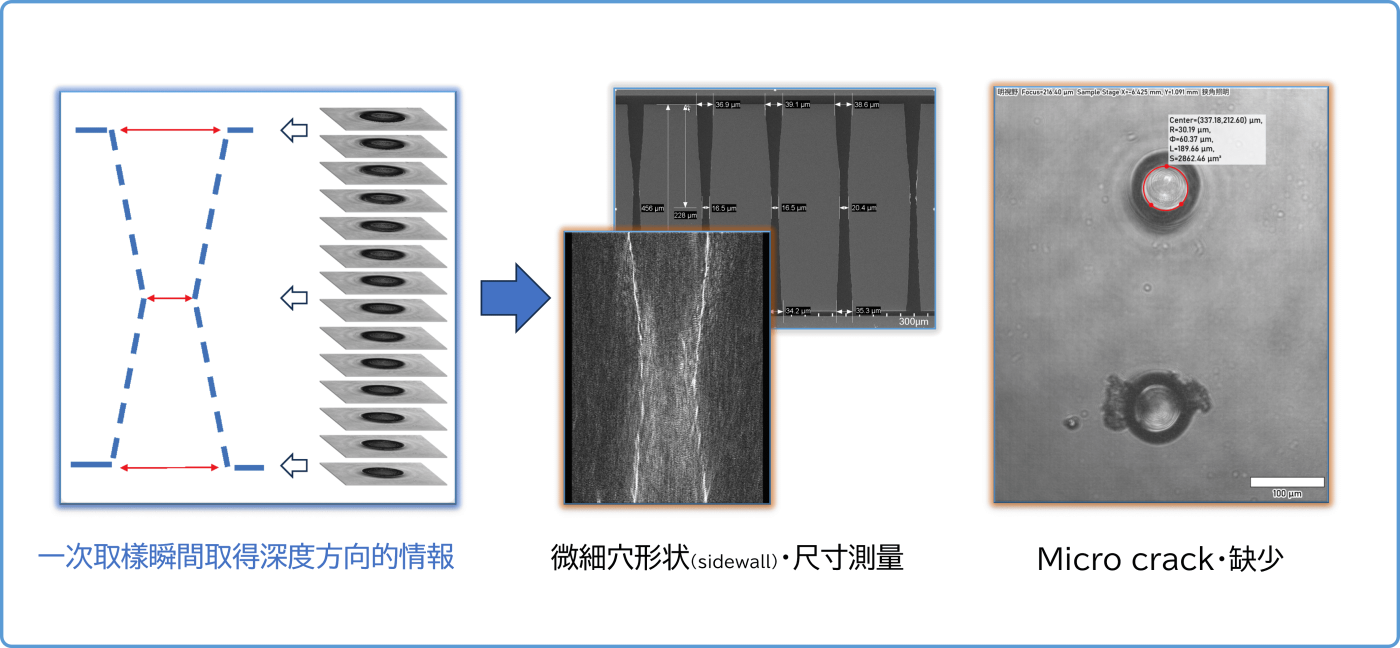

TGV開孔量測推薦

光波動場3D顯微鏡 MINUK可在單次量測(2秒)內取得所有3維深度方向的的資訊,並得到孔徑形狀,對位,缺陷Crack等等所有資訊。無須對焦,在單次量測中可以將最高1400μm深度,以最細2μm分割,並得到Z方向的nm級成像。

相關產品

其他相關訊息

-

06.Dec.2022

CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!

-

01.Aug.2022

【薄膜厚度量測】『顯微分光法』與『橢圓偏光法』有什麼不同?

-

25.Mar.2025

半導體薄膜製程是什麼?6大技術提升良率,專業應用優勢多!