依據歐盟施行的個人資料保護法,我們致力於保護您的個人資料並提供您對個人資料的掌握。 我們已更新並將定期更新我們的隱私權政策,以遵循該個人資料保護法。請您參照我們最新版的 隱私權聲明。

本網站使用cookies以提供更好的瀏覽體驗。如需了解更多關於本網站如何使用cookies 請按 這裏。

06Dec.2022

膜厚儀

CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!

| 目錄 1.CMP是什麼意思?製程中可應用在哪些環節? 2.CMP製程技術與原理介紹 3.CMP製程如何應用在環節中? a.CMP製程關鍵材料|研磨液的粒徑與界達電位 b.CMP製程關鍵研究|晶圓表面電位與研磨液及清潔劑的交互作用 c.CMP製程即時監控|架設於研磨機內部即時監控研磨厚度 d.CMP製程成果發表|研磨後膜厚分佈量測 |

CMP是什麼意思?製程中可應用在哪些環節?

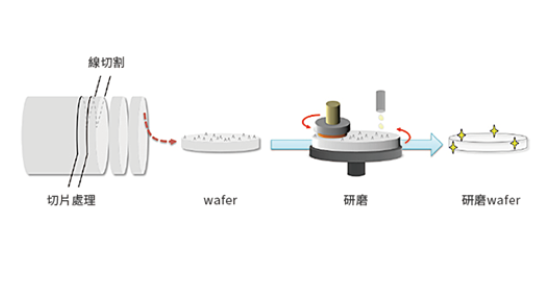

所謂的「CMP」,意為「化學機械研磨,Chemical-Mechanical Polishing」的縮寫。是指使用研磨劑(Slurry),將晶圓減薄或是鏡面化的一道工藝。一般在半導體前段製程中,會使用化學腐蝕與機械加工的方式,歷經反覆地曝光顯影蝕刻所形成的微電路中。如果在每一道製程下,卻有表面平整度不均與凹凸不平的缺陷,將會影響最終成品的良率與效率。故CMP製程,則是讓反覆製程堆疊造成的高低誤差減少或是去除,讓製程中的晶圓基材或鍍膜材料表面厚度減薄的一種方式。

而在半導體製程日益精進的今日,從一開始的類比IC、記憶體到邏輯IC的產品推進中,每一世代從1.3毫米~3奈米的產品複雜度與日俱增,使用到CMP製程的頻率更甚以往。 在半導體反覆鍍膜後,利用CMP製程將多餘的厚度給移除後再鍍上另外一層;如同建造高樓大廈般,在每一層的堆疊中,CMP製程是用來精準控制每一層鍍膜高度的最佳監工。

CMP製程除了厚度控制以外,最後進行的表面拋光也是CMP一道手續。將已經研磨至目標厚度的晶圓表面殘留物去除(也有人稱為鏡面加工),以亮晶晶的表面迎接下一道半導體製程。一般來說,CMP製程中會有下列環節:

| 將被研磨物放置貼合至於研磨底盤Pad |

⬇

| CMP研磨液注入 |

⬇

| 設置轉速、研磨時間、目標厚度... |

⬇

| 開始研磨拋光 |

⬇

| 研磨結束後清洗 |

CMP製程技術與原理介紹

在CMP製程中,能否精準地將多餘厚度移除,主要是取決於幾種重要的零部件;研磨頭Disk、研磨墊底盤Pad與研磨液Slurry,皆會影響研磨製程好壞的重要因素。在良好的CMP製程中,CMP研磨頭Disk的研磨顆粒細緻度,會直接影響研磨後待測物表面的平整度(粗糙度Ra);研磨墊底盤Pad與樣品的黏貼均一性,也會影響整個樣品研磨後的上下表面是否為水平狀。

而CMP研磨液Slurry,更是CMP研磨中不可或缺的潤滑劑與散熱材。可根據不同的研磨目標,選用不同種類的研磨液,例如:不同粒徑大小、不同種類粒子、不同組成溶液等等。

| 關鍵因素 | 影響 | |

|---|---|---|

| CMP研磨頭Disk | 研磨頭細緻度 | 研磨後的平整度(粗糙度Ra) |

| CMP研磨墊Pad | 黏貼均一性 | 研磨樣品的水平 |

| CMP研磨液Slurry | 粒徑大小、電位正負與晶圓的關係 | 研磨效果 |

| CMP清潔液Cleaner | 電位正負與晶圓的關係 | 清潔效果 |

在研磨的產品中,又有分單面拋光與雙面拋光:

- 單面拋光:指在上面加以一平均分散的機械力於單一方向的旋轉後,使待測物表面以固定速率來移除表面的厚度

- 雙面拋光:是指待測物的正面&反面各施予反方向的旋轉的機械力來研磨,並依據實際產品的需要,而使用各自符合的方式來達成其減薄目的

CMP製程如何應用在環節中?

👉 CMP製程關鍵材料|研磨液的粒徑與界達電位

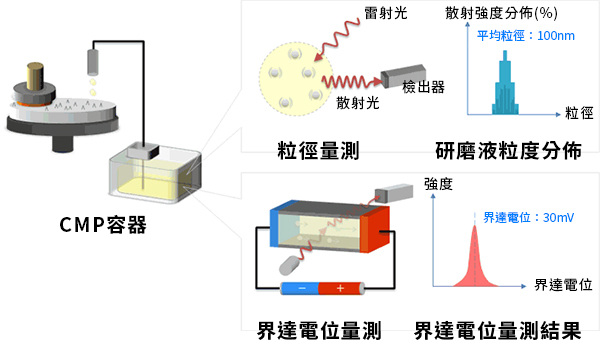

講到CMP製程中不可或缺的就是-CMP研磨液,品質不佳的研磨液可能會讓晶圓表面直接變身月球表面。根據不同研磨程度,選用不同大小及種類的研磨液。大塚的ELSZ系列為業界普遍採用的界達電位粒徑分析機種,具有強大的感度以及穩定性幫您監控研磨液的穩定度。

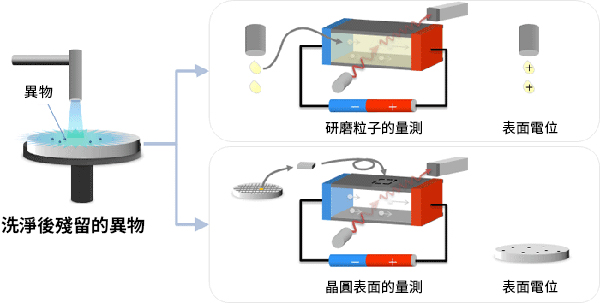

👉 CMP製程關鍵研究|晶圓表面電位與研磨液及清潔劑的交互作用

除了研磨液以外,被研磨的對象晶圓本身表面電位也是一個重要的參數。為了控制晶圓與研磨液的關係,表面電位也是一個重要指標。大塚獨家的固體表面電位量測,可直接量測晶圓的表面電位,更可以自由更換液相成份讓你得到晶圓<=>研磨液,或晶圓<=>清潔劑的交互作用。且除了晶圓本身以外,也可研究研磨底盤Pad的電位喔!

👍推薦閱讀: 界達電位量測原理介紹,固態樣品表面電位(surface zeta potential)量測方法與實踐-->

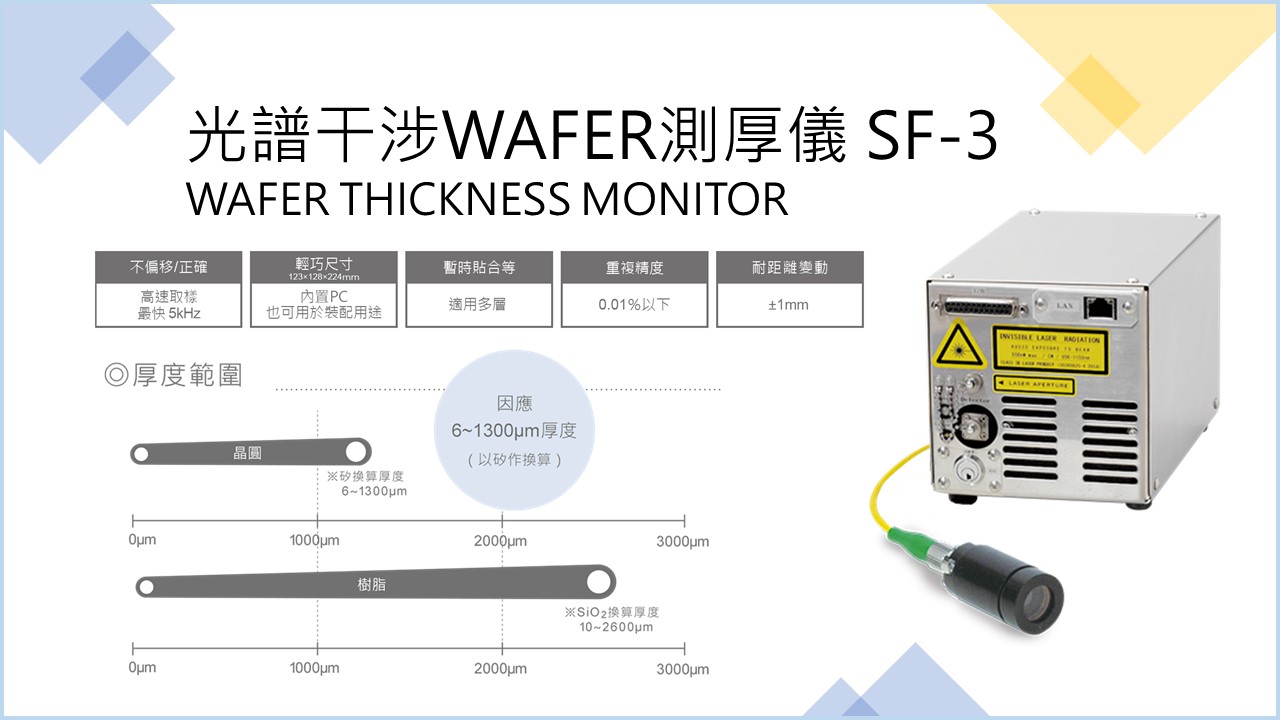

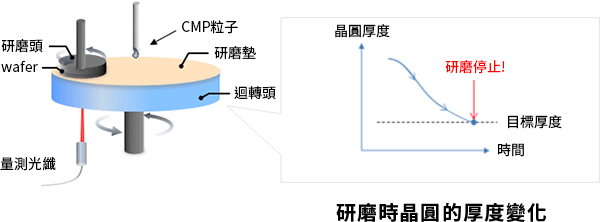

👉 CMP製程即時監控|架設於研磨機內部即時監控研磨厚度

針對於半導體基材不管是Si、GaAs、GaN、SiC等,皆可使用CMP方式使其材表面平坦化。大塚使用其獨自開發的光學膜厚量測技術,可針對上述所提到的各種半導體基材做即時研磨監控與厚度管理。

特別是SF-3晶圓即時量測單元,利用強度穩定之半導體雷射於正面量測反射率,可直接內藏於各種製程設備中,並針對基材厚度做real time的基材厚度量測。可輕鬆得到應用高速研磨的CMP設備中,單點量測的時間低最低可以達到μs等級。

不只是單層基材構造可以對應,針對半導體於3D IC封裝時其晶背減薄厚,也能夠輕易地將上層Si減薄層的厚度量出。量測精度方面,更是超越目前市面上其他量測方式的結果。另外,還可搭配小光斑20um的量測點位,可透過CCD對位的方式,針對樣品表面特定之Pattern量測定點厚度量測。

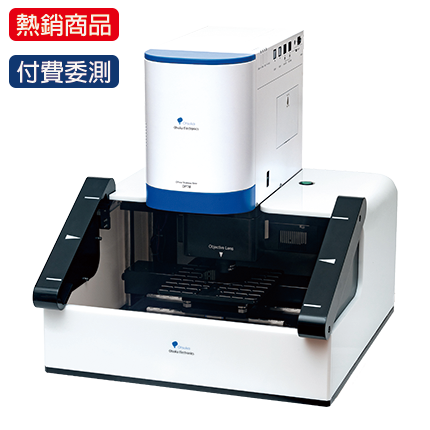

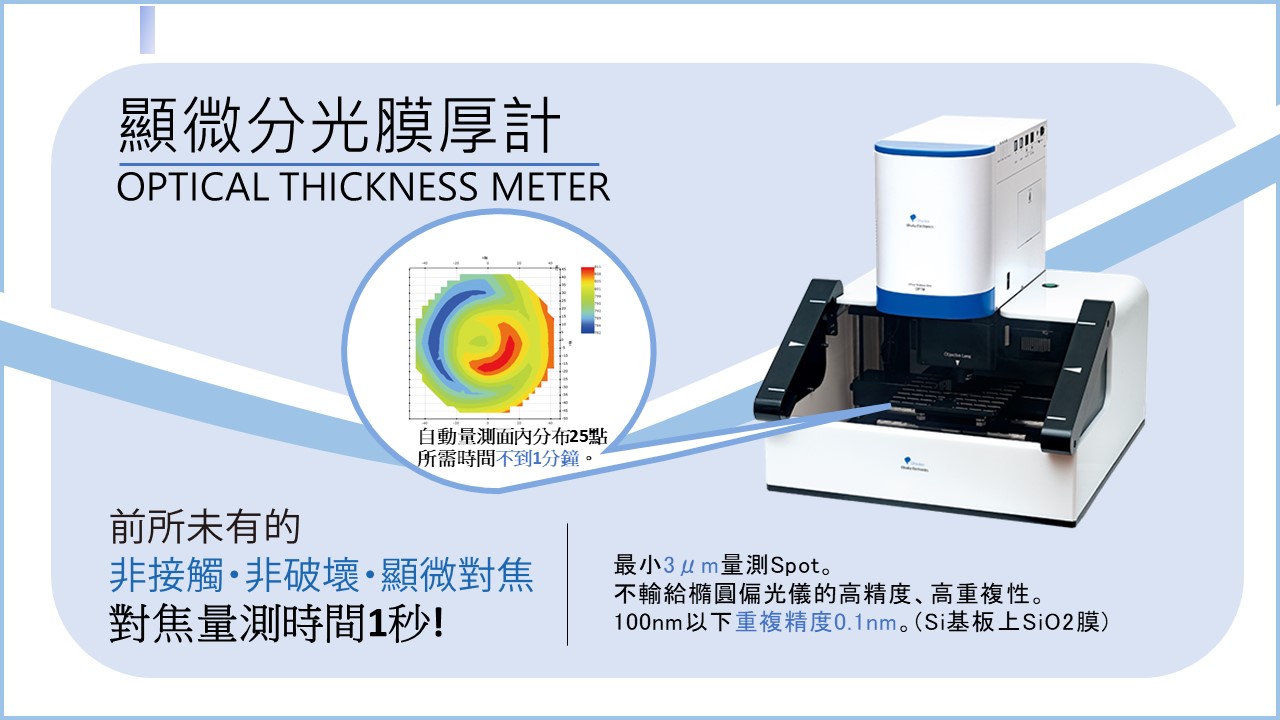

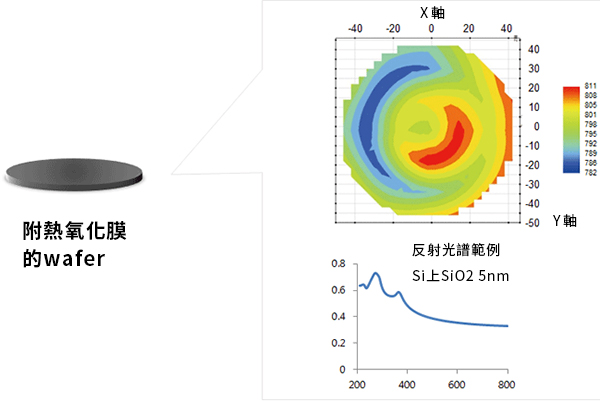

👉 CMP製程成果發表|研磨後膜厚分佈量測

針對薄膜鍍膜製程後,在CMP製程中上層減薄厚度的量測,也有高膜厚精度顯微分光量測儀OPTM可以對應。並使用正反射的方式依膜厚需求選配對應之波長範圍(可從UV紫外光波段到NIR近紅外光波段),完全可以支援針對一般鍍膜工程所需要的膜厚量測範圍10-10000A。

其量測精度誤差在A(0.1nm)等級,單點量測時間可以在一秒內完成。同樣搭配高倍率的光學顯微系統,可以量測spot size光斑依照規格(最小可以縮小到3um),再搭配自動定位Auto alignment的功能,自動定位量測點位到樣品表面任何待測Pattern位置。並依據實際產線需求,給予In-situ 或是 standalone型式做選擇,提供產線自動化SECS/GEM的通訊協定支援。

成立於1970年的大塚電子,在2003年進入臺灣成立-大塚科技,致力於將本身具備的厚實光學量測技術導入,以「光」為中心研發出各項量測需求,並提供客戶最佳的解決方案。若對於CMP製程還有相關的疑問,不妨就直接到聯絡我們填寫表單,將會有專人為你服務喔!

相關產品

其他相關訊息

-

01.Aug.2022

【薄膜厚度量測】『顯微分光法』與『橢圓偏光法』有什麼不同?

-

25.Mar.2025

半導體薄膜製程是什麼?6大技術提升良率,專業應用優勢多!

-

29.Aug.2024

光學膜(Optical Film)是什麼?6大產業應用要知道,推薦機型看這邊!