半導體應用技術文章

-

06Dec.2022

CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!

CMP是什麼意思?製程中可應用在哪些環節?

讓你快速了解CMP製程的相關內容與應用! -

05Dec.2022

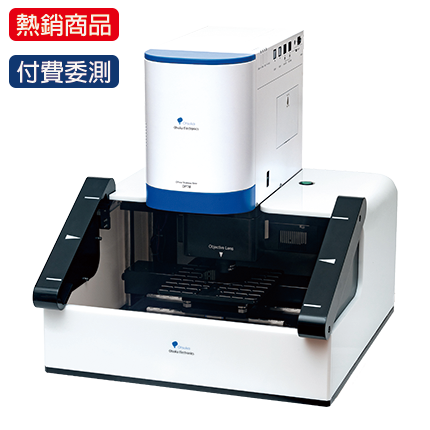

【光學膜厚量測】高速晶圓面內mapping膜厚管理

OPTM以對焦時間短見長(單點1秒以下),以單片晶圓中量測面內25點為例所需時間為1分鐘內。

活用其快速的量測時間特性,不管是在產線或是一般實驗室中都能大幅提高工作效率。 -

10Jan.2022

【光學膜厚量測】多層結構矽晶圓減薄研磨膜厚量測

當晶圓進行研磨或蝕刻減薄厚度時,進行即時厚度監控;可於線上確認研磨厚度,不須停機確認,提高製成效率。

-

23Jan.2024

矽穿孔(TSV)孔徑底材膜厚量測介紹:深入了解TSV製程及原理,知道製品優勢在那裡

在現今科技快速發展之下,TSV(Through-Silicon Via)技術已成為三維積體電路(3D IC)中不可或缺的一環。然而,當TSV的尺寸與結構也越來越精細,這對其孔徑底材膜厚的量測也提出了新的挑戰。TSV孔徑底材膜厚量測,對於確保TSV製程的品質與可靠性至關重要。如果你對於TSV孔技術還是一知半解的話,不妨就透過本文來了解其技術創新發展吧!

-

21Sep.2023

光干涉原理是什麼?5大應用範疇,專家帶你深入了解!

光干涉原理,可涉及到光學和材料科學等多個學科。且在各種技術和工業領域中,也都有著廣泛的應用,例如:光學儀器的校準、生物醫學成像與精密的物質測量等。當兩束或多束同頻率的光波在相同的空間中重疊時,由於它們的相位差異,會產生明暗交替的干涉條紋。而這種現象不僅揭示了光的波動性,更為現代科技帶來了無數的校準與應用的可能性!

-

21Jun.2023

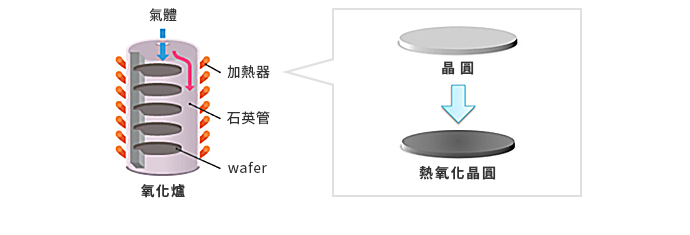

半導體製程順序大公開!專家用11步驟告訴你,專業技術大解密!

許多人對於半導體產業不熟悉,尤其是對半導體製程的概念更是一知半解?!其實,主要是用來製作晶片的半導體製程,是需要透過一系列的專業步驟與搭配粒徑以及饃厚量測後,才能被完整的運用在各個產業之中。若你對於半導體製程還是有許多疑問的話,不妨就一起透過本篇專家的講解來了解吧!

-

06Dec.2022

CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!

CMP是什麼意思?製程中可應用在哪些環節?

讓你快速了解CMP製程的相關內容與應用! -

05Dec.2022

【光學膜厚量測】高速晶圓面內mapping膜厚管理

OPTM以對焦時間短見長(單點1秒以下),以單片晶圓中量測面內25點為例所需時間為1分鐘內。

活用其快速的量測時間特性,不管是在產線或是一般實驗室中都能大幅提高工作效率。 -

10Jan.2022

【光學膜厚量測】多層結構矽晶圓減薄研磨膜厚量測

當晶圓進行研磨或蝕刻減薄厚度時,進行即時厚度監控;可於線上確認研磨厚度,不須停機確認,提高製成效率。

-

23Jan.2024

矽穿孔(TSV)孔徑底材膜厚量測介紹:深入了解TSV製程及原理,知道製品優勢在那裡

在現今科技快速發展之下,TSV(Through-Silicon Via)技術已成為三維積體電路(3D IC)中不可或缺的一環。然而,當TSV的尺寸與結構也越來越精細,這對其孔徑底材膜厚的量測也提出了新的挑戰。TSV孔徑底材膜厚量測,對於確保TSV製程的品質與可靠性至關重要。如果你對於TSV孔技術還是一知半解的話,不妨就透過本文來了解其技術創新發展吧!

-

21Sep.2023

光干涉原理是什麼?5大應用範疇,專家帶你深入了解!

光干涉原理,可涉及到光學和材料科學等多個學科。且在各種技術和工業領域中,也都有著廣泛的應用,例如:光學儀器的校準、生物醫學成像與精密的物質測量等。當兩束或多束同頻率的光波在相同的空間中重疊時,由於它們的相位差異,會產生明暗交替的干涉條紋。而這種現象不僅揭示了光的波動性,更為現代科技帶來了無數的校準與應用的可能性!

-

21Jun.2023

半導體製程順序大公開!專家用11步驟告訴你,專業技術大解密!

許多人對於半導體產業不熟悉,尤其是對半導體製程的概念更是一知半解?!其實,主要是用來製作晶片的半導體製程,是需要透過一系列的專業步驟與搭配粒徑以及饃厚量測後,才能被完整的運用在各個產業之中。若你對於半導體製程還是有許多疑問的話,不妨就一起透過本篇專家的講解來了解吧!